延迟线(Delay Line)用于引入一个可调的延迟,用来对信号的时序进行精确控制。在 DDR 控制器中,延迟线的精确性非常关键,因为它直接影响信号的同步性,尤其是在处理高速时钟信号时。

1. 延迟线(Delay Line)校准概述

- 延迟线校准触发

- 在 PLL 锁定 后,延迟线的校准可以通过 PIR 寄存器 来触发。

- 该校准是确保时钟信号与 DDR 时钟同步的关键步骤,必须在高频初始化任务之前完成。

- 延迟线校准的绕过

- 绕过校准:通过 PIR 寄存器 中的 DCALPSE 位,可以跳过延迟线校准。

- 注意:绕过后需要确保在后续的操作中手动触发校准,否则内存访问等操作可能会失败。

- 延迟线独立校准(

重点)- 每个 LCDL(Local Calibrated Delay Line) 都是一个独立的延迟单元,负责调整某个信号路径中的延迟。由于每个 LCDL 可能应用于不同的功能(例如,数据路径、命令路径等),它们的电路特性、负载和工作环境可能会有所不同。因此,每个 LCDL 都需要独立进行校准,以确保它们各自的延迟精度。

- 校准的过程中,会通过测量每个 LCDL 中的延迟步骤数量,来确保它的输出延迟与目标时钟(DDR 时钟)的周期完全一致。**”延迟步骤”** 指的是延迟线内部的可调延迟单位(

cell),通常是时钟周期的一个子集。通过校准,我们可以确定需要多少个延迟步骤,才能使得该延迟线的延迟时间与 DDR 时钟的周期相匹配。- 例如,如果 DDR 时钟的周期是 1ns,延迟线可能有多个可调节的延迟步骤(如每个步骤为 0.1ns),校准后可以知道需要 10 步来获得 1ns 的延迟。

- 延迟线校准时机

- 通常在 PHY 初始化 阶段进行,作为整个系统初始化的一部分,确保时钟信号同步。

- 用户也可以通过 PIR 寄存器的 DCAL 位,随时手动触发延迟线的校准。

- 延迟线校准的重要性

- 延迟线校准确保系统在电压、温度变化时,延迟线仍然能保持稳定的时延,避免时序错误。

- 校准控制

- 延迟线的校准操作可以被 用户 控制,通过设置 PIR 寄存器 的相关位(如 DCAL)触发或绕过校准。

- 在校准过程中,MDL(主延迟线) 会定期进行周期测量,并通过公式计算出补偿后的延迟值。

2. LCDL校准的基本结构与原理

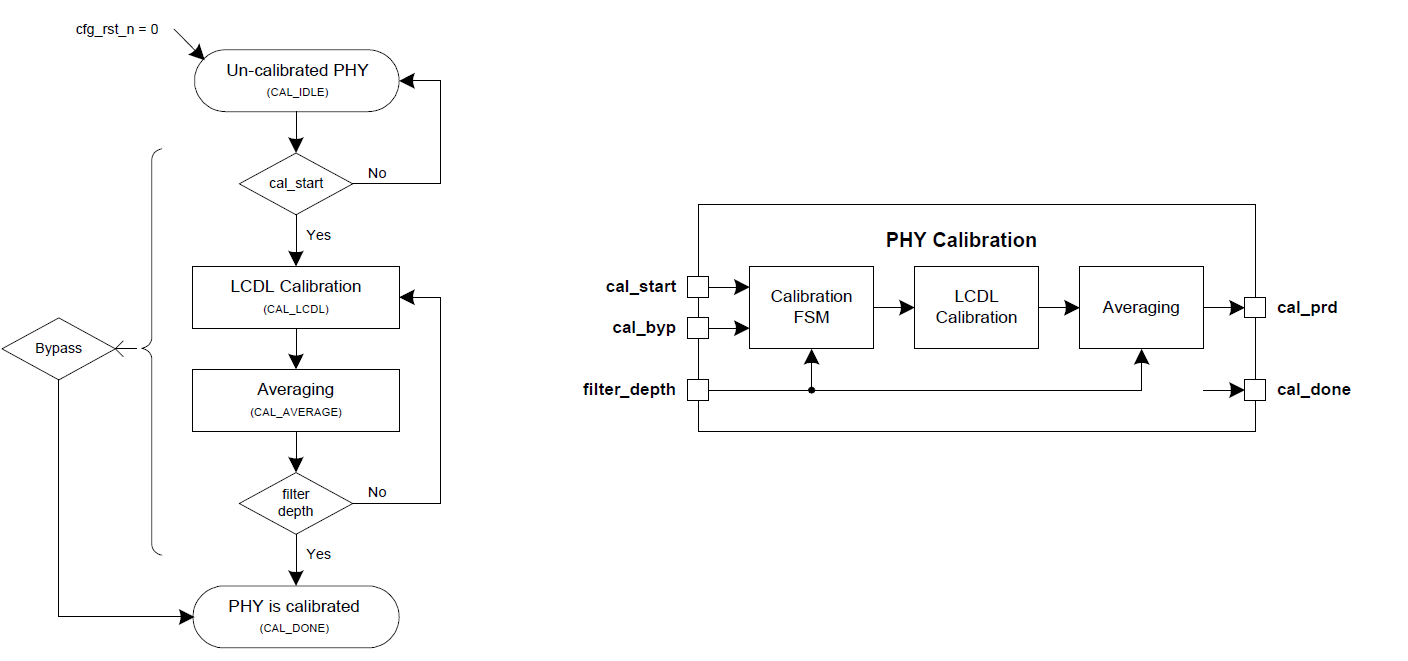

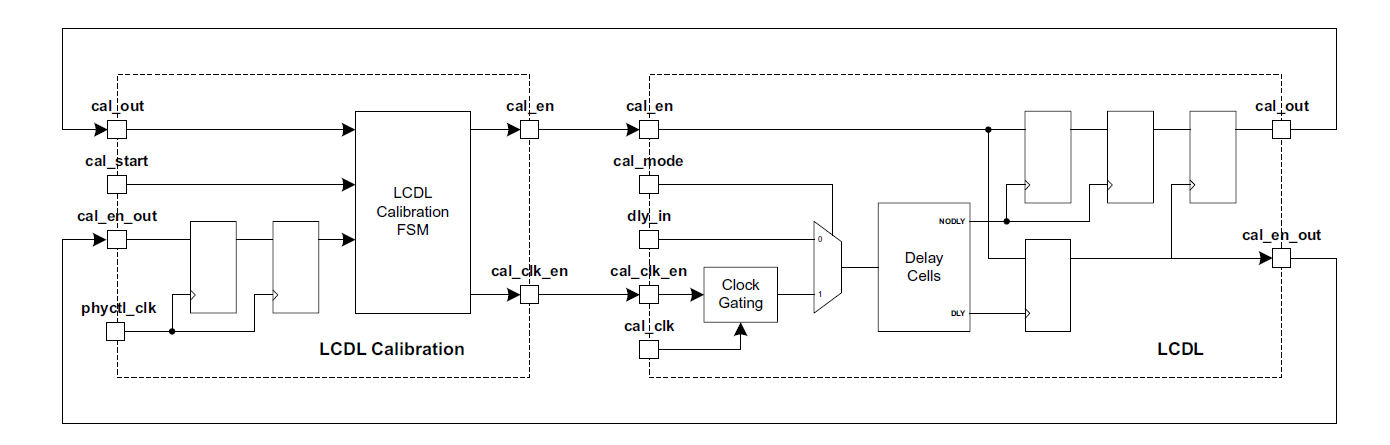

- LCDL校准链路图:描述了LCDL与PHY内部的其他模块之间的连接,主要涉及到在LCDL与LCDL状态机之间进行周期测量。该过程由更高层的校准逻辑触发,通常是一个状态机,执行LCDL的周期测量。

- 校准流:LCDL校准状态机(FSM,Finite State Machine)会启动LCDL的测量,并采样每个延迟设置下的测量结果,直到延迟值与时钟周期匹配。

3. 校准过程详细步骤

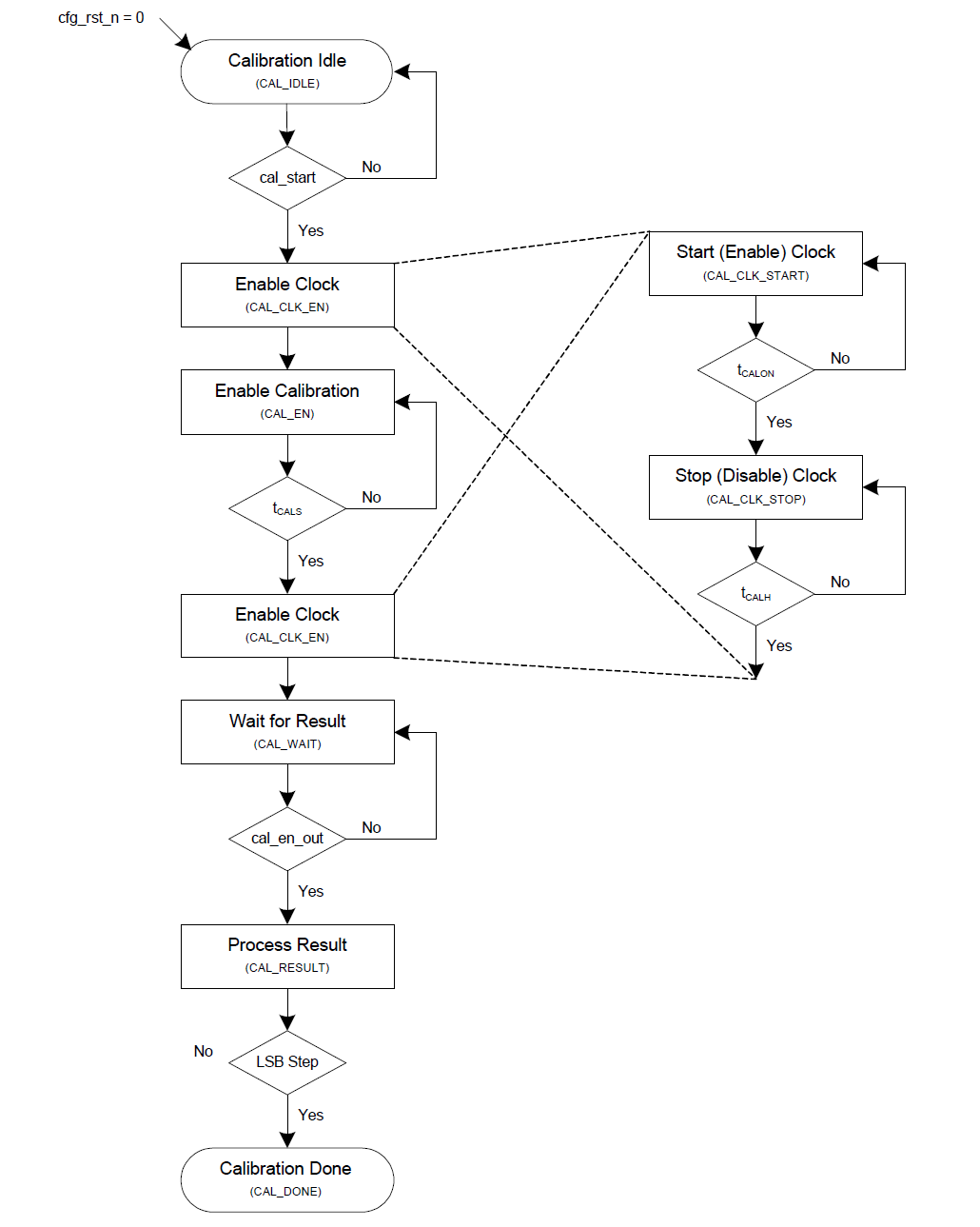

步骤1:复位与初始设置

- 在配置复位期间(例如,当

cfg_rst_n信号被置为有效时),LCDL状态机会处于空闲状态,直到复位解除。 - 复位解除后,状态机继续保持在空闲状态,直到从主校准状态机收到校准触发信号。此时,LCDL状态机会开始执行校准操作。

- 在空闲状态,延迟选择的初始值设置为LCDL最大值的一半。LCDL状态机采用二分查找算法来确定最合适的延迟设置。

步骤2:时钟复位

- 在开始进行周期测量之前,先启用校准时钟到LCDL,但不启用实际的测量过程。这一步是为了重置LCDL内部的测量触发器(flip-flops)。

- 校准时钟会在一定的时间内启用,这个时间由

PTR2.tCALON定义,校准时钟启用一段时间后会被关闭。然后进入等待状态,等待一定的时间PTR2.tCALH,之后才能进入下一步。

步骤3:启用测量逻辑

- 在时钟复位后,启用校准测量逻辑。通过使能

cal_en信号来启动测量过程。PTR2.tCALS定义了启用信号的设定时间,确保信号能够稳定后再开始时钟启用。

步骤4:等待测量完成

- 状态机(FSM)会监视

cal_en_out信号,直到它被置为有效。这个信号的上升沿意味着校准时钟已经通过LCDL的延迟单元,并注册了校准启用信号cal_en,从而表明测量操作已经完成。 cal_en_out信号会在使用前与PHY控制域时钟同步。

步骤5:评估测量结果

- 测量完成后,状态机会根据测量结果判断延迟是否需要增加或减少。如果测量结果为1,则说明延迟超过了一个时钟周期,需要减少延迟。如果测量结果为0,则说明延迟小于一个时钟周期,需要增加延迟。

步骤6:继续二分查找或线性搜索

- 二分查找:当延迟选择值的变化达到最大值(即已加或减去1的延迟值)时,搜索完成。

- 线性搜索:当检测到

cal_out信号的上升沿,或者已测试过最小或最大延迟选择值时,搜索完成。 - 如果搜索没有完成,状态机会返回步骤2,重新调整延迟值并再次进行测量,直到找到合适的延迟设置。

流程图

本文作者:

ICXNM-ZLin

本文链接: https://talent-tudou.github.io/2024/10/27/DDR/PUB Architecture-Delay Line Calibration and Control/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!

本文链接: https://talent-tudou.github.io/2024/10/27/DDR/PUB Architecture-Delay Line Calibration and Control/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!